# Garmin Power Sensor Test Fixture

PROJECT PLAN

Group Number | May 1729 Jeramie Vens | Client Dr. Degang Chen | Advisor Amna Aftab | Key Concept Holder #1 Brandon Floyd | Team Leader Stephen Julich | Webmaster Francis Wagner | Team Communication Leader Xi Zhu | Key Concept Holder #2 <u>bjfloyd@iastate.edu</u> | Team Email http://may1729.sd.ece.iastate.edu | Team Website

Revised: October 2016/Version 1

## Contents

1 Introduction

1.1 Project statement

<u>1.2 purpose</u>

1.3 Goals

2 Deliverables

<u>3 Design</u>

3.1 Previous work/literature

3.2 Proposed System Block diagram

3.3 Assessment of Proposed methods

3.4 Validation

4 Project Requirements/Specifications

4.1 functional

4.2 Non-functional

5 Challenges

<u>6 Timeline</u>

6.1 First Semester

6.2 Second Semester

6.3 Team Duties

7 Conclusions

8 References

9 Appendices

# 1 Introduction

#### **1.1 PROJECT STATEMENT**

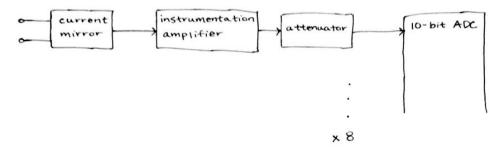

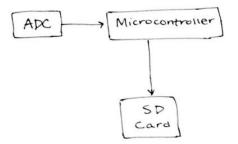

During product development at Garmin, engineers want to be able to measure the power consumed by parts of their circuits in their fitness electronics. Our power sensor fixture will have eight channels with two probes capable of measuring currents from 10  $\mu$ A to 10 mA and voltages from 0 to 5.5 V. We will use a microcontroller to calculate power consumption with the aforementioned measurements and an SD card to store the measurements. Garmin engineers hope to hook up our fixture to a gadget and let it run overnight.

#### **1.2 PURPOSE**

Fitness electronics are driving a healthier society. Garmin is a leader in this market, and we are providing a tool that will allow engineers to not only work more efficiently but also to work with more information. This information allows them to make more informed design choices that will lead to a safe, useful electronic device.

#### 1.3 GOALS

First and foremost, we want to handle our business with class and thoughtfulness. We hope to work professionally with our client and advisor from start to finish. Meeting deadlines will make for a smooth design process. The cost of each board should not exceed \$300. We should have a prototype in hand before the end of the first semester. We should be able to measure current within our four established ranges with less than 1% error. With a couple of manual adjustment portions of our circuit, we should make the design dummy-proof in the event of an ill-advised adjustment. We want to increase accuracy and performance in our second design based on the tests we perform on our prototype. We want to get our client a finished, working product by the end of the semester.

## 2 Deliverables

By Thanksgiving Break, we will send our CADSTAR design to Garmin to develop a prototype PCB. Our client has said that we will receive the prototype during Winter Break. After testing the board and optimizing measurements and errors, we will send our final CadStar design to Garmin by Spring Break. On top of the final PCB, we will deliver detailed, easy-to-follow documentation.

# 3 Design

Our design includes op-amp circuit design, ADC integration, and microcontroller programming. We will consider cost, performance, robustness, and user-friendliness.

#### 3.1 Previous work/literature

Power measurements are nothing new, and our design is driven by a specific Garmin need within their prototype engineering testing phase of their fitness electronics division.

#### 3.2 PROPOSED SYSTEM BLOCK DIAGRAM

Input

#### **3.3 Assessment of Proposed methods**

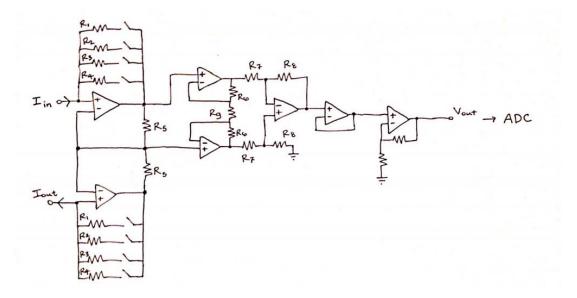

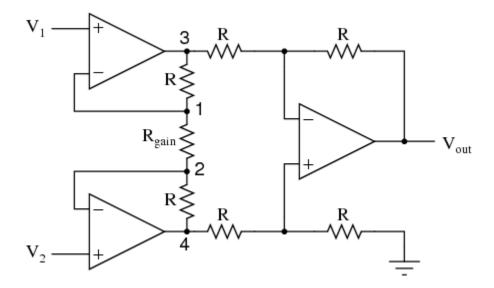

Our first major task is to measure current without affecting the current value, and we will accomplish this with a current mirror circuit. There are two options for current mirrors - one involves bipolar junction transistors and the other just involves operational amplifiers. Because our understanding of BJTs is elementary and because we do not sacrifice a great deal of performance without BJTs, we chose the design that involves only op amps.

We then pondered how to offset the error of resistor values as the exactitude of the current mirror depends on the equivalence of the resistors. Our initial thought was to get digital potentiometers involved, but the performance of digital pots can be unpredictable. Instead of digital potentiometers, we will use manual potentiometers. Our project will be used by capable engineers, so we trust that a one-time manual adjustment would be preferable to the intense troubleshooting that could accompany an on-the-fritz digital pot.

In order to measure currents in a range from 10  $\mu$ A to 100 mA, we need different resistor values within our mirror circuit. Instead of using at least four times as many op amps to cover different ranges, we decided to use switches. We considered programmable relays, but once again our client assured us that the engineers could manually switch the ranges because they would have a good idea of what range their circuits would fall into.

Our final major circuit design consideration depended on the ADC's parameters. Shown above is an instrumentation op amps coming off of the mirror circuit. This design means there would be eight inputs to the ADC - one voltage measurement for each channel. Knowing which resistor value is switched on, we can calculate input voltage, input current, and input power with the microcontroller.

#### 3.4 VALIDATION

Once we receive the prototype, our first test will be measuring the output current given an input current. We will hope for a low error, and our second design will focus largely on minimizing the difference in said currents. On top of our current concerns, our client will provide a sample fitness electronic from which to take measurements.

# 4 Project Requirements/Specifications

#### 4.1 FUNCTIONAL

- Measure currents from 10 uA to 100 mA

- Measure voltages from 0 to 5.5 V

- Convert voltage range to 0 to 3.3 V before ADC

- Use microcontroller to compute power consumption with above measurements

- Replicate first channel circuit to bring channel total to 8

- Use SD card to store large amounts of data

#### 4.2 Non-functional

- Thorough, specific documentation

- Sleek, aesthetically pleasing PCB

## 5 Challenges

Our client has a generous budget, so cost considerations are the least of our worries. Having said that, we will avoid wasteful spending whenever possible.

Materials available to us are limited by what Garmin has to offer. Luckily, they have plenty to offer.

Implementing a file system for the Cortex M microprocessor that supports a file size greater than 4 GB could be a challenge if library support does not exist.

It may be necessary to implement calibration routines for the hardware if testing indicates it is necessary. This work has been pushed to the second semester. Integrating this functionality may significantly impact previous programming work.

The range of the current needed to measure is very small. we need to collaborate all the resistance in order to get the accurate current measurement in all ranges.

In this project, we need to design 8 channels for different ranges. It may be challenging to fit all components on our PCB, which will be about 30 square inches.

### 6 Timeline

#### 6.1 FIRST SEMESTER

We will have a prototype back from Garmin's manufacturers by the end of the first semester. See Gantt chart below for details.

#### 6.2 Second Semester

We will perform test on our prototype and use the results to have a design submitted to Garmin by Spring Break. We will have our final PCB in hand by mid-April. See Gantt chart below for details.

| Task | Description                             |  |  |  |  |  |  |  |

|------|-----------------------------------------|--|--|--|--|--|--|--|

| 1    | Develop prototype PCB circuit design    |  |  |  |  |  |  |  |

| 2    | Develop project plan                    |  |  |  |  |  |  |  |

| 3    | Receive manufactured design from Garmin |  |  |  |  |  |  |  |

| 4    | Test manufactured PCB circuit           |  |  |  |  |  |  |  |

| 5    | Optimize the circuit                    |  |  |  |  |  |  |  |

| 6    | Create documentation for the circuit    |  |  |  |  |  |  |  |

| 7    | Prepare midterm presentation            |  |  |  |  |  |  |  |

| 8    | Create design document                  |  |  |  |  |  |  |  |

| 9    | Prepare final presentation              |  |  |  |  |  |  |  |

|                    | First Semester |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

|--------------------|----------------|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|--------------|------|------|--------|--------|

|                    |                |     |     |     |     |     |     |     |     |      |      |      |      | Thanksgiving |      |      | Finals |        |

| PROJECT TIMELINE   |                |     |     |     |     |     |     |     |     |      |      |      |      | Break        |      |      | Week   | Winter |

|                    | WK1            | WK2 | WK3 | WK4 | WK5 | WK6 | WK7 | WK8 | WK9 | WK10 | WK11 | WK12 | WK13 | WK14         | WK15 | WK16 | WK17   | Break  |

| Anticipated TASK 1 |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Actual Task 1      |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Anticipated TASK 2 |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Actual Task 2      |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Anticipated TASK 3 |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Actual Task 3      |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Anticipated TASK 4 |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Actual Task 4      |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Anticipated TASK 5 |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Actual Task 5      |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Anticipated TASK 6 |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Actual Task 6      |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Anticipated TASK 7 |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Actual Task 7      |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Anticipated TASK 8 |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Actual Task 8      |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Anticipated TASK 9 |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| Actual Task 9      |                |     |     |     |     |     |     |     |     |      |      |      |      |              |      |      |        |        |

| PROJECT TIMELINE   | Second Semester |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

|--------------------|-----------------|-----|-----|-----|-----|-----|-----|--------|----------|------|------|------|------|------|------|------|--------------|

|                    |                 |     |     |     |     |     |     | Spring |          |      |      |      |      |      |      |      | Final        |

|                    |                 | WK2 | WK3 | WK4 | WK5 | WK6 | WK7 | Break  | WK9      | WK10 | WK11 | WK12 | WK13 | WK14 | WK15 | WK16 | Presentation |

| Anticipated TASK 1 |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Actual Task 1      |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Anticipated TASK 2 |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Actual Task 2      |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Anticipated TASK 3 |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Actual Task 3      |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Anticipated TASK 4 |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Actual Task 4      |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Anticipated TASK 5 |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Actual Task 5      |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Anticipated TASK 6 |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Actual Task 6      |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Anticipated TASK 7 |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Actual Task 7      |                 |     |     |     |     |     |     |        | -        |      |      |      |      |      |      |      |              |

| Anticipated TASK 8 |                 |     |     |     |     |     |     |        | <u> </u> |      |      |      |      |      |      |      |              |

| Actual Task 8      |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Anticipated TASK 9 |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Actual Task 9      |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

| Actual Task 9      |                 |     |     |     |     |     |     |        |          |      |      |      |      |      |      |      |              |

#### 6.3 TEAM DUTIES:

Amna Aftab, Brandon Floyd, Francis Wagner, and Xi Zhu will make most of the electrical engineering decisions and Stephen Julich will make most of the computer engineering decisions.

Amna Aftab will note the key concepts discussed in meetings.

Brandon Floyd will handle the majority of the correspondence with our client and advisor.

Stephen Julich will keep the website on track.

Francis Wagner will handle the lion's share of the documentation.

Xi Zhu will conduct the transfer of designs from paper to CadStar.

# 7 Conclusions

After considering all realistic available design paths and taking the counsel of our client and advisor into account, we have settled on a circuit design. We will build this circuit on breadboards in order to perform basic performance tests. Once we are comfortable with the results of said tests, our goal is to formalize a design with CadStar before Fall Break. Our prototype will be manufactured by Garmin based on our CadStar design.

Optimization will be the name of the game once we have a prototype. In addition to minimizing error and maximizing performance, the computer engineering aspects of our project will come to the forefront in the second semester. When we are confident that we have an optimized design that meets all client specifications, we will send a second CadStar design to Garmin by Spring Break in order to receive our final PCB for our presentation. We will know that we have done our jobs if Garmin engineers use our project during the testing phases of their fitness electronics designs.

## 8 References

#### **Circuit Design**

http://www.allaboutcircuits.com/textbook/semiconductors/chpt-8/the-instrumentation-amplifier/

**PCB Design**

Cadstar tutorial(pdf):

http://www.cpv-systemhaus.com/downloads/CADSTAR\_Kendin\_Ogren.pdf

Cadstar online video tutorial:

https://www.youtube.com/playlist?list=PLho9wAgXSO4S\_tWzGSaZY85VFAkZ2gJh6

https://www.youtube.com/playlist?list=PL45B8973C31EB35F9

https://www.youtube.com/playlist?list=PLho9wAgXSO4SE-x\_UaCXKtxSXuaWBr0dc

#### FRDM-KL25Z Board, ARM Cortex M0 Microprocessor, SD Card Standards, ADC

FRDM Board Schematic

Kinetis Design Studio User's Manual

KL25 Sub Family Reference Manual

SD Standard Overview

ADC Overview

## 9 Appendices

We do not need this section for Version 1.